### Features

- Operating voltage: 4.5V~5.5V

- LCD driving voltage: 8V~16V

- Applicable LCD duty cycle from 1/8 to 1/64

### Applications

- Electronic dictionaries

- Portable computers

- Suitable for various types of LCD panel

- Bias voltage adjustable from an external source

- Remote controllers

- Calculators

# **General Description**

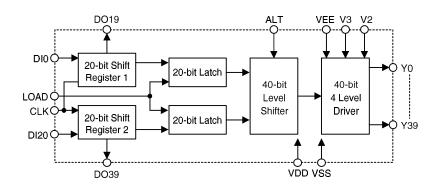

The HT1602 is a dot matrix LCD segment driver LSI implemented in CMOS technology. It is equipped with a 40-bit shift register (two 20-bit shift registers), a 40-bit latch (two 20-bit latches), a 40-bit level shifter, a 40-bit 4-level driver, and control circuits.

The HT1602 can convert serial data received from an LCD controller to parallel data and

# **Block Diagram**

then send them out as LCD driving waveforms to the LCD panel. The HT1602 can be applied up to 1/64 duty. Furthermore, the bias voltage which determines the LCD driving voltage can be optionally supplied from an external source, thus the chip is suitable for driving various types of LCD panel. These special features increase the versatility of the chip.

1

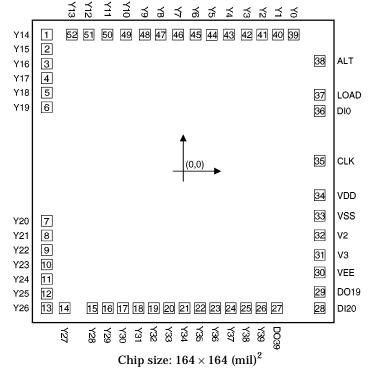

#### **Pad Assignment**

\* The IC substrate should be connected to VDD in the PCB layout artwork.

#### **Pad Coordinates**

Y Pad No. Y Pad No. Y Pad No. Х Х Х -76.2376.23 19 -16.61-76.2337 75.78 42.66 1 2 -76.2368.13 20 -8.10-76.2338 75.78 61.56 3 -76.2360.03 21 0.5 -76.2339 61.20 76.23 4 -76.2351.93 22 9.10 -76.2340 52.56 76.23 -76.23 -76.23 5 43.83 23 17.60 41 43.65 76.23 6 -76.2335.73 24 26.15 -76.2342 35.10 76.23 7 -76.23-27.6325 34.70 -76.2343 25.20 76.23 8 -76.23-35.7326 43.25 -76.2344 15.71 76.23 9 -76.23-43.8327 51.89 -76.2345 6.66 76.23 10 -76.23-76.2376.23 -51.9328 75.78 46 -3.0611 -76.23-60.0329 75.78 -67.1447 -12.8376.23 -76.23-68.1330 75.78 -56.34-21.6076.23 12 48 -76.23-76.2331 76.23 13 75.78 -46.6249 -32.04-66.33-76.2332 -35.64-42.4876.23 14 75.78 50 -50.81-76.23-52.9215 33 75.78 -24.7551 76.23 -42.26-76.2334 75.78 -13.3252 -62.1576.23 16 17 -33.71-76.2335 75.78 6.03 -76.2318 -25.1636 75.78 33.66

2

Unit: mil

# **Pad Description**

| Pad No. | Pad Name | I/O | Description                                      |  |  |  |

|---------|----------|-----|--------------------------------------------------|--|--|--|

| 1~26    | Y14~Y39  | 0   | LCD driver outputs for segments*                 |  |  |  |

| 27      | DO39     | 0   | Shift register output for the 40th bit data      |  |  |  |

| 28      | DI20     | Ι   | Input data of shift register 2                   |  |  |  |

| 29      | DO19     | 0   | Shift register output for the 20th bit data      |  |  |  |

| 30      | VEE      | Ι   | LCD power supply                                 |  |  |  |

| 31, 32  | V3, V2   | Ι   | LCD bias supply voltage                          |  |  |  |

| 33      | VSS      | _   | Negative power supply                            |  |  |  |

| 34      | VDD      | _   | Positive power supply                            |  |  |  |

| 35      | CLK      | Ι   | Clock pulse input for the shift register         |  |  |  |

| 36      | DI0      | Ι   | Input data of shift register 1                   |  |  |  |

| 37      | LOAD     | Ι   | Latching signal to latch shift register data     |  |  |  |

| 38      | ALT      | Ι   | Alternate input signal for LCD driving waveforms |  |  |  |

| 39~52   | Y0~Y13   | 0   | LCD driver outputs for segments*                 |  |  |  |

\*: For Y0~Y39, any of VDD, V2, V3 or VEE can be selected as a display driving source according to the combination of latched data level and ALT signal. Refer to the following table:

| Latched Data | ALT | Display Data Output Leve |  |  |

|--------------|-----|--------------------------|--|--|

| н            | Н   | $V_{\rm EE}$             |  |  |

| п            | L   | V <sub>DD</sub>          |  |  |

| т            | Н   | V3                       |  |  |

| L            | L   | V2                       |  |  |

## **Absolute Maximum Ratings\***

| Supply Voltage | 0.3V to 6V                            |

|----------------|---------------------------------------|

| Input Voltage  | $V_{SS}0.3V$ to $V_{DD}\mbox{+-}0.3V$ |

| Storage Temperature–50°C to $125^\circ\text{C}$ |  |

|-------------------------------------------------|--|

| Operating Temperature20°C to 70°C               |  |

\*Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

3

Ta=25°C

# D.C. Characteristics

| Shal             | Parameter            | Test Conditions |            | Min.               | True | Max.        | Unit |

|------------------|----------------------|-----------------|------------|--------------------|------|-------------|------|

| Symbol           | Farameter            | VDD             | Conditions | <b>WIIN.</b>       | Тур. | Max.        | Unit |

| V <sub>DD</sub>  | Operating Voltage    | _               | _          | 4.5                |      | 5.5         | V    |

| I <sub>DD</sub>  | Operating Current    | 5V              | No load    | _                  | 100  | 300         | μΑ   |

| ISTB             | Standby Current      | 5V              | —          |                    | 1    | 5           | μΑ   |

| flcd             | Max. Clock Frequency | 5V              | _          | 3.3                | _    |             | MHz  |

| twclk            | Clock Pulse Width    | 5V              | _          | 125                |      |             | ns   |

| V <sub>IL</sub>  | "L" Input Voltage    | 5V              | _          |                    | _    | $0.2V_{DD}$ | V    |

| V <sub>IH</sub>  | "H" Input Voltage    | 5V              | _          | 0.8V <sub>DD</sub> | _    | _           | V    |

| V <sub>LCD</sub> | LCD Driving Voltage  | 5V              |            | 8                  |      | 16          | V    |

28th Aug '98

4

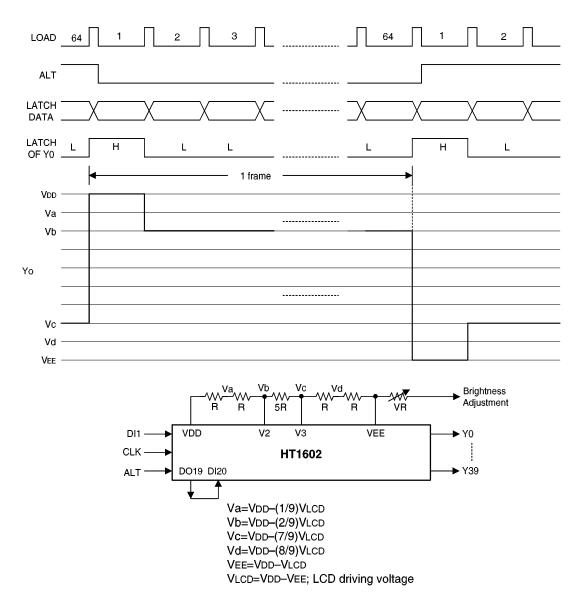

## **Timing Diagrams**

1/64 duty and 1/9 bias (with the ALT changing polarity for every frame, a frame=64 commons)

28th Aug '98

5

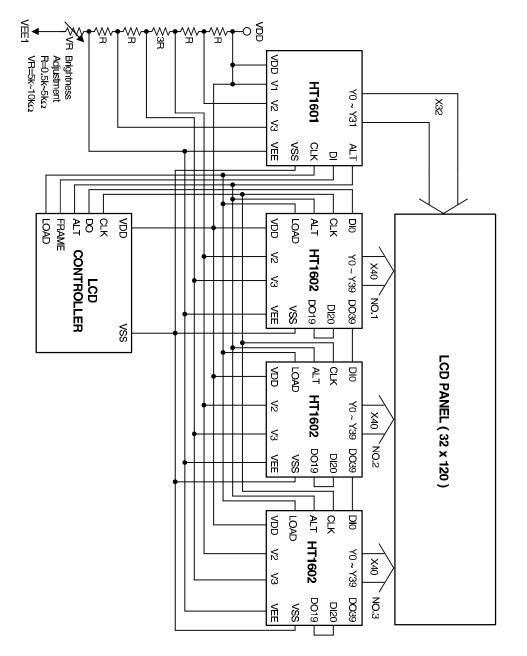

# **Application Circuits**

1/32 duty and 1/7 bias

6